# Комплексная параметризация геометрических моделей микроэлектронных объектов

П. М. Ширяев, С. Э. Миронов, В. А. Павлов

Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. В.И. Ульянова (Ленина)

pshir2000z@gmail.com, semironovspb@yandex.ru

Аннотация. Для трехмерных микроэлектронных объектов и иерархических систем разного уровня сложности предлагается технология автоматизированного проектирования широкого спектра вариантов реализации их двумерных геометрических моделей (их топологических чертежей). Это обеспечивается оригинальными методами и средствами параметризации описания геометрических проектирования. всех уровнях на их электрическая параметризация Технологическая И обеспечивается автоматизированной системой сжатия геометрических моделей микроэлектронных объектов. Схемотехническая и топологическая параметризация системой генерации геометрических моделей по схеме на алгоритмов размещения и трассировки. структурная параметризация - средствами структурной кластеризации геометрических моделей иерархических объектов и средствами управляемого иерархического уплотнения геометрических моделей объектов.

Ключевые слова: геометрические модели микроэлектронных объектов; параметризация моделей; сжатие геометрических моделей; размещение и трассировка; высокая плотность упаковки

### Проектирование геометрических моделей микроэлектронных объектов

Одними из наиболее сложных систем являются интегральные схемы, оперативная разработка которых невозможна без применения средств автоматизации и библиотек проектных решений. Однако огромное число вариантов реализации, определяемых широким многообразием параметров, характеризующих каждый из компонентов микроэлектронных систем на многочисленных этапах ИХ разработки, невозможным создание библиотеки геометрических моделей (топологии) микроэлектронных объектов и систем на все случаи жизни. Выходом из этой ситуации может быть только разработка технологии комплексной параметризация геометрических микроэлектронных объектов и систем и создание на ее основе библиотеки параметризированных программных автоматизированного проектирования геометрических моделей микроэлектронных объектов и систем.

Параметризация микроэлектронных систем подразумевает возможность настройки их геометрической модели на многочисленные векторы параметров:

- структурно-топологические (разрядности данных, структурный план иерархической микроэлектронной системы);

- схемотехнические (электрические схемы компонентов микроэлектронной системы);

- электрические (параметры компонентов микроэлектронной системы – длина и ширина каналов транзисторов, ширины шин);

- топологические (принципы организации геометрических моделей ячеек – расположение шин и транзисторов, соотношение габаритов компонентов, расположение их выводов);

- технологические (минимально допустимые размеры компонентов нижнего уровня проектирования всех типов, зазоры между компонентами, включение одного компонента в другой компонент, выход одного компонента за пределы другого).

Наиболее многочисленна последняя группа параметров, которая в последние десятилетия приобрела особую значимость. Это связано с постоянной модернизации полупроводниковых технологий и производств [1], что породило новое направление в системах автоматизированного проектирования, связанное с адаптацией геометрических моделей к требуемым проектным нормам.

Это способ упрощения и ускорения процесса разработки, связанный с абстрагированием топологии от конструкторско-технологических требований (КТТ). Это обеспечивает долговечность проектов благодаря возможности их оперативной адаптации к требуемым проектным нормам выбранного предприятияизготовителя. Это позволяет при разработке топологии ячеек сосредоточиться на решении задачи взаимного расположения элементов без утомительной детальной проработки топологии под КТТ. Технология настройки проекта на КТТ называется сжатием топологии, и уменьшение предполагает расстояния отдельными компонентами в соответствии с вектором технологических параметров.

реализации эффективна Для этого подхода методология символьного проектирования. Ее базовый элемент – «символ»: параметризируемый примитив, абстрактно описывающий элемент или группу элементов через комбинацию слоев. Классическим примером символа является МОП-транзистор, определяемый ключевыми параметрами виртуальными значениями длины канала, абстрагированными ширины И конкретных от проектных норм.

Топологические описания (геометрические модели) всех микроэлектронных объектов, представляющие собой их двумерные геометрические модели, могут быть параметризированы, а процесс их проектирования автоматизирован [2]. Причем учет особенностей объектов каждого уровня топологической иерархии позволяет повысить эффективность (плотность упаковки

и время генерации топологии) методов и средств проектирования.

разработке При геометрических моделей микроэлектронных объектов и систем разного уровня приходится заниматься сложности вопросами системного проектирования, требующими индивидуальных особенностей каждого из компонентов системы и учета их взаимного влияния. Поэтому основными задачами при работе над технологией комплексной параметризации геометрических моделей микроэлектронных объектов являются мониторинг параметров моделей, анализ значений параметров и их модификация.

При этом непрерывно совершенствуются методы и средства систем автоматизированного проектирования, разрабатываются новые методологии [3] оптимизируются вычислительные алгоритмы. Одной из таких методологий, о которой пойдет речь, является иерархическое проектирование макроблоков (сложных фрагментов) БИС, основанное на разработке геометрических моделей использованием c иерархического описания их структуры. Этот подход позволяет декомпозировать сложный процесс проектирования на управляемые уровни.

## II. ПРОЕКТИРОВАНИЕ ГЕОМЕТРИЧЕСКИХ МОДЕЛЕЙ СЛОЖНЫХ МИКРОЭЛЕКТРОННЫХ ОБЪЕКТОВ

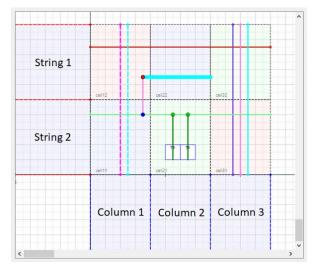

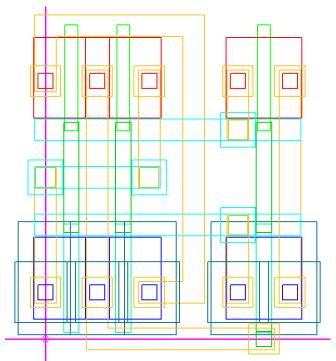

Процесс проектирования сложных иерархических микроэлектронных объектов начинается с этапа построения их структурированной иерархической геометрической модели (структурно-топологического плана) в графическом редакторе, разработанной авторами системы автоматизированного проектирования иерархических геометрических моделей сложных микроэлектронных объектов и систем (рис. 1).

Рис. 1. Окно графического редактора автоматизированной системы структурно-топологического проектирования иерархических геометрических моделей сложных микроэлектронных объектов

Как видно из рис. 1, при проектировании плана тополог прорисовывает шины земли, питания и основных сигналов (как магистральные, так и локальные межъячеечные). Это позволяет упростить и ускорить процесс генерации топологии отдельных ячеек, исключая из него рассмотрение заведомо неэффективных вариантов.

На основании созданной иерархической структурно топологической модели макроблока редактор генерирует

два типа описаний: спецификации макроблока и его компонентов и шаблоны ячеек. Спецификации макроблока и его модулей (строк и столбцов) отражают состав и взаимное расположение модулей в макроблоке и ячеек в модуле. Спецификации ячеек описывают расположение их границ и выводов (рис. 2). Эта информация необходима для оригинальной САПР управляемого иерархического сжатия Matching of cells [4]. Она настраивает топологию на требуемые проектные нормы, согласовывает габариты и расположение выводов ячеек и собирает топологию макроблока. Шаблоны ячеек (рис. 3) содержат описание размещенных в границах ячеек компонентов (шин контактов и транзисторов) и используются в качестве «заготовок» для системы генерации топологии ячеек. Таким образом, исходными данными для средств размещения и трассировки [5] компонентов топологии ячейки служат ее электрическая схема, спецификация и шаблон.

```

CPA_cell22_rht -- rht -- 10.00

CPA_cell22_top -- top -- 7.00

M2_cell22_rht -- rht -- 6.00

cell22top -- lft -- 0.00

cell22top -- rht -- 15.00

cell22bot -- lft -- 0.00

cell22bot -- rht -- 15.00

cell22left -- btm -- 0.00

cell22left -- top -- 12.00

cell22right -- btm -- 0.00

cell22right -- top -- 12.00

```

Рис. 2. Пример спецификации ячейки в окне графического редактора автоматизированной системы структурно-топологического проектирования иерархических геометрических моделей сложных микроэлектронных объектов

OR(NORTH) CPA (22.0,24.0) W\_Contact(10); OR(NORTH) CPA (30.0,22.0) W\_Contact(10); Wire(M2) W\_WIRE(-3) (30.0,18.0)-(15.0,18.0);

Рис. 3. Пример шаблона ячейки в окне графического редактора автоматизированной системы структурно-топологического проектирования иерархических геометрических моделей сложных микроэлектронных объектов

Далее каждая ячейка автоматизировано наполняется компонентами-символами с помощью генератора топологий, создающего абстрактное представление, без привязки к конкретным топологическим нормам. Символами являются модели транзистора, шины и контакта.

После генерации символьных топологий всех ячеек САПР «Matching of cells» осуществляет согласование ячеек в требуемых проектных нормах (обеспечивая корректное взаимное расположение и соединение соседних ячеек) и сборку топологии макроблока.

Обязательным финальным этапом является всесторонняя верификация. Основные проверки включают в себя контроль технологических норм (DRC) и схемотопологическую верификацию, которая подтверждает соответствие топологии исходной схеме.

Успешное прохождение верификации позволяет считать топологию готовой к производству.

### III. АВТОМАТИЗИРОВАННАЯ ГЕНЕРАЦИЯ ГЕОМЕТРИЧЕСКИХ МОДЕЛЕЙ ЯЧЕЕК

Генерация геометрической модели ячейки выполняется на основе трех ключевых описаний: формализованной спецификации ячейки, шаблона топологии ячейки и ее электрической схемы. Спецификация описывает интерфейс (границы положение выводов). Шаблон топологии описывает расположение части ее компонентов (транзисторы, шины и контакты), размещенных в топологии разработчиком структурно-топологического плана. Электрическая схема точно набор описывает транзисторов устройства и их соединения.

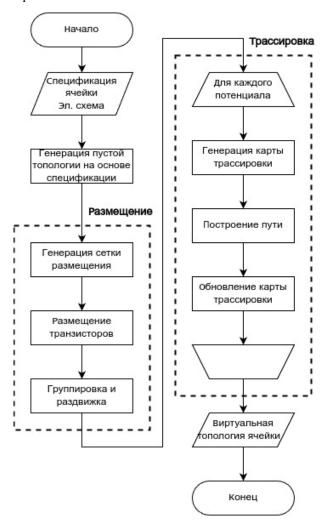

Алгоритм процесса генерации топологии представлен на рис. 4.

Рис. 4. Алгоритм генерации топологий

Процесс автоматизированной генерации включает этапа: размещение и трассировку. два основных Размещение оптимизирует пространственное расположение транзисторов внутри границ ячейки, учитывая площадь и подготовку к трассировке. Трассировка формирует проводящие пути, реализующие соединения из электрической схемы, с соблюдением минимальных зазоров и ширины проводников во избежание конфликтов и минимизации паразитных эффектов. Центральными сущностями пропесса являются netlist и виртуальная топология. Netlist -

формальное описание электрических связей. Виртуальная топология представляет собой абстрактное представление структуры ячейки в виде координатной сетки. Эта сетка кодирует обобщенные правила и относительные отношения проектирования для КМОПтехнологии (допустимые позиции, шаги, направления трассировки), абстрагируясь от абсолютных значений конкретных КТТ. Такая абстракция обеспечивает гибкость и переносимость на этапе синтеза. Физическая реализация по конкретным КТТ достигается позже на этапе сжатия.

Ключевые сущности виртуальной топологии включают четыре базовых класса:

- Транзисторы (*Transistor*) моделируют активные элементы с параметрами ширины канала (w), ориентации и подключения исток/сток/затвора к сигнальным сетям (потенциалам);

- Проводники (Wire) описывают трассировочные пути на заданных слоях (Poly, M1-M2), электрически связывая элементы, относящиеся к одной сигнальной сети;

- Контакты (*Contact*) обеспечивают вертикальные соединения на металлическом слое с указанием координат и идентификатор сигнала;

- Межслойные переходы (Via) реализуют соединения между разными слоями через строго типизированные варианты с координатной привязкой.

Второй ключевой сущностью процесса является электрическая схема ячейки, формально описываемая в netlist. Netlist представляет структурированный текстовый файл, содержащий два основных типа информации: перечень всех транзисторов с их типами и детальное описание электрических связей между ними через именованные сигнальные сети. Этот файл служит строгой и однозначной спецификацией функционального поведения ячейки на уровне компонентов и их соединений. Как основной входной генератора топологии, ДЛЯ непосредственно определяет, какие элементы должны быть размещены и как они должны быть соединены на физическом уровне.

### А. Размещение транзисторов

Этап размещения транзисторов представляет собой процесс оптимизации пространственного расположения активных элементов в границах проектируемой ячейки. Основной целевой метрикой данного этапа является взвешенная оценка качества на основе взаимного расположения транзисторов.

Алгоритм размещения транзисторов [6] основан на анализе совместимости соседних транзисторов на ортогональной координатной сетке. Целью алгоритма служит максимизация пар транзисторов с объединенными диффузионными областями и общими затворами, что сокращает площадь и длину соединений. Для больших схем вводится ограничение времени работы с выбором лучшего найденного варианта.

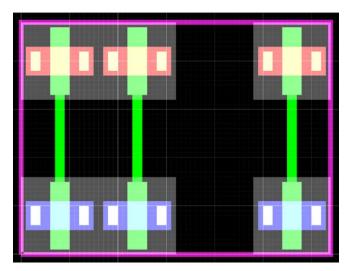

Пример виртуальной топологии мультиплексора после этапа размещения представлен на рис. 5.

Рис. 5. Виртуальная геометрическая модель после этапа размещения транзисторов

### В. Трассировка

Этап трассировки неразрывно связан с этапом размещения транзисторов, поскольку пространственная конфигурация размещенных элементов непосредственно определяет сложность, длину И реализуемость межсоединений. Неоптимальное расположение транзисторов (например, чрезмерная разбросанность функционально связанных элементов, образование "узких мест" или конфликтующих зон) неизбежно приводит к усложнению траекторий проводников, увеличению их паразитных параметров и, в критических случаях, к невозможности корректной трассировки без нарушения технологических правил.

Алгоритм трассировки [7] реализует маршрутизацию на трехмерной координатной сетке, моделирующей слои межсоединений, включая слой поликремния. Ключевым аспектом является оптимизация порядка трассировки: (потенциалы) с наибольшим количеством соединяемых точек обрабатываются в первую очередь, что повышает вероятность успешной прокладки сложных соединений. Система поддерживает работу с ориентированными слоями, где каждому слою металла могут быть назначены предпочтительные направления трассировки, например, горизонтальное для M1, вертикальное для М2. Количество используемых слоев металла является настраиваемым параметром; при этом слои, расположенные ближе к кремниевой подложке (например, M1), обладают более высоким приоритетом при назначении ресурсов для трассировки по сравнению с вышележащими слоями. Этот приоритет обусловлен стремлением минимизировать длину критичных соединений и снизить паразитные эффекты.

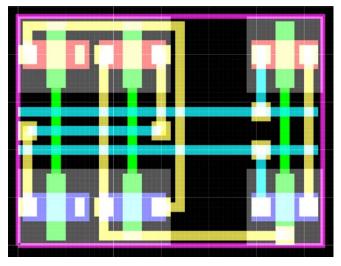

Визуальное представление виртуальной топологии после этапа трассировки представлено на рис. 6.

Для дальнейшей работы виртуальная топология экспортируется в формат системы сжатия *TopDesign*.

### IV. Сжатие топологии и Схемо-топологическая верификация

### А. Сжатие

После генерации виртуальной топологии ячейки, она передается в САПР-среду *TopDesign* [8]. Основная задача этого этапа — выполнение операции сжатия. В ходе сжатия виртуальная топология, заданная в

обобщенных координатах и правилах, преобразуется в физическую геометрию, соответствующую КТТ целевого производственного процесса.

Рис. 6. Виртуальная геометрическая модель микроэлектронного объекта после этапа трассировки

Система *TopDesign* представляет собой инструментальную среду комплексной параметризации проектирования фрагментов СБИС, охватывающую все уровни — от информационного до технологического. Результат сжатия представлен на рис. 7.

Рис. 7. Результат работы автоматизированной системы управляемого иерархического сжатия геометрических моделей объектов с учетом вектора технологических параметров

# В. Верификация

Верификация сформированной топологии критически представляет собой важный этап проектирования. Для обеспечения функциональной корректности И соответствия исходной схеме применяется инструмент схемо-топологической верификации. В качестве входных данных для проверки используются:

- Исходный netlist ячейки, идентичный тому, что применялся на этапе генерации топологии, задающий эталонное электрическое поведение;

- Физическая реализация топологии в стандартном формате *CIF*, содержащая геометрическое описание всех слоев и элементов после этапа сжатия.

Сравнение этих двух артефактов позволяет однозначно установить соответствие между электрической схемой и ее физической реализацией, гарантируя корректность проектного решения перед передачей на производство.

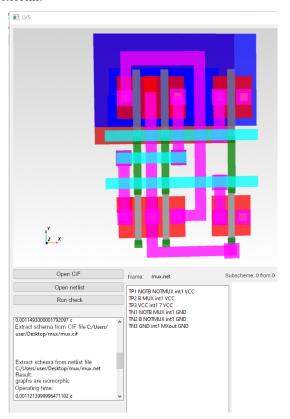

Для верификации топологии используется программа [9], реализующая формальный графовый подход. Она выполняет три ключевых шага: построение графа из электрической схемы, построение графа из схемы, извлеченной из физической топологии, и поиск изоморфизма между этими графами для установления их структурного соответствия. Такой метод обеспечивает строгое и математически обоснованное сравнение функциональности исходной схемы и ее физической реализации.

На рис. 8 представлен результат верификации топологии.

Рис. 8. Результат процесса автоматического мониторинга и сравнительного анализа геометрической и электрической моделей микроэлектронного объекта

### V. ЗАКЛЮЧЕНИЕ

В представленной работе предложен и реализован комплексный подход к автоматизированному проектированию топологий ячеек БИС, основанный на символьном описании и алгоритмической генерации. Ключевым вкладом является разработка метода генерации, интегрирующего комбинаторное размещение

транзисторов и адаптивную трассировку на многослойной сетке.

параметризация Комплексная проекта осуществляется программными средствами на разных уровнях проектирования, что снижает сложность средств генерации результирующей топологии. В редакторе структурно-топологических планов (который формирует данные для САПР управляемого иерархического сжатия Matching of cells) можно задавать разрядность данных макроблока и топологические особенности реализации макроблока и его ячеек. Варианты схемных решений могут быть заданы (или заменены) путем выбора их netlist из библиотеки схем. В параметризации электрических характеристик компонентов (ширина шин, ширина и длина канала транзистора) задействованы средства генерации топологии ячеек и система сжатия TopDesign. Системы TopDesign и Matching of cells позволяют параметризировать проектные нормы.

Модульная архитектура системы обеспечивает гибкость: новые алгоритмы размещения, трассировки или верификации могут быть интегрированы без перепроектирования ядра. Предложенный полхол сокращает время разработки топологий гарантированном соблюдении технологических норм и электрических характеристик. Реализация в виде инструментального комплекса, включая интеграцию со средой TopDesign для сжатия и с программным модулем для верификации, подтверждает его практическую применимость в проектировании БИС.

### Список литературы

- I.L. Markov, J. Hu and M.-C. Kim, "Progress and Challenges in VLSI Placement Research," in Proceedings of the IEEE, vol. 103, no. 11, pp. 1985-2003, Nov. 2015, doi: 10.1109/JPROC.2015.2478963.

- [2] S. E. Mironov, K. M. Zibarev. Complex parameterization technology for topological projects of regular VLSI macroblocks. Problems of advanced micro- and nanoelectronic systems development. Russia, 2020, pp. 35-40. 10.31114/2078-7707-2020-3-35-40.

- [3] S. Sabbavarapu et al., "A Novel Physical Synthesis Methodology in the VLSI Design Automation by Introducing Dynamic Library Concept," 2013 International Symposium on Electronic System Design, Singapore, 2013, pp. 103-107, doi: 10.1109/ISED.2013.27.

- [4] S.E. Mironov, A.Y. Vasiliev, "Controlling the process of coordination of complex layout objects of microelectronic systems in conditions of uncertainty of design rules," 2017 IEEE II International Conference on Control in Technical Systems (CTS), St. Petersburg, 2017, pp. 192-195, doi: 10.1109/CTSYS.2017.8109523.

- [5] Ziesemer A., Lazzar C. Transistor level automatic layout generator for non-complementary CMOS cells, 2007 IFIP International Conference on Very Large Scale Integration, Atlanta, GA, USA, 2007, pp. 116-121, doi: 10.1109/VLSISOC.2007.4402483

- [6] Ширяев П.М., Миронов С.Э. Алгоритм плотноупакованного размещения транзисторов, учитывающий особенности топологической реализации ячеек БИС // Изв. СПбГЭТУ «ЛЭТИ». 2024. Т. 17, № 9. С. 46-52. doi: 10.32603/2071-8985-2024-17-9-46-52.

- [7] Ширяев П.М., Миронов С.Э. Оптимизация трассировки ячейки БИС в условиях неопределенности // XXVIII Международная конференция по мягким вычислениям и измерения. 2025. с. 123-126. doi: 10.1109/SCM66446.2025.11060254.

- [8] Зуев И.С. САПР TopDesign виртуального символьного проектирования параметризованных фрагментов КМОП БИС // Изв. СПбГЭТУ «ЛЭТИ». 2016. № 7. С. 23-31

- [9] Варфоломеев А.С., Лепов. А.В., Миронов С.Э. Верификация электрических и геометрических моделей с помощью алгоритмов проверки графов на изоморфизм // XXVIII Международная конференция по мягким вычислениям и измерения. 2025. с. 118-122. doi: 10.1109/SCM66446.2025.11060105.