# Технология анализа и верификации геометрических моделей микроэлектронных объектов

А. С. Варфоломеев, Е. Д. Ботова, В. Н. Буряков, А. А. Когутенко, С. Э. Миронов, П. М. Ширяев

Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. В.И. Ульянова (Ленина)

semironovspb@yandex.ru

Аннотация. Описываются средства методы И мониторинга и анализа геометрических моделей (топологии) микроэлектронных объектов и иерархических систем разного уровня сложности. Для анализа качества геометрических моделей предлагается комплексный критерий, и описываются оригинальные программные средства мониторинга характеристик, их анализа и Приводится описание средств соответствия геометрической модели исходному описанию объектов и средств анализа соответствия геометрической модели параметрам технологической реализации.

Ключевые слова: верификация топологии; анализ качества геометрических моделей; схемная верификация; технологическая верификация

# I. ВЕРИФИКАЦИЯ ТОПОЛОГИИ МИКРОЭЛЕКТРОННЫХ ОБЪЕКТОВ

С ростом сложности разрабатываемых микроэлектронных объектов и иерархических систем растет вероятность появления ошибок на различных этапах проектирования их геометрических моделей (топологических шаблонов). Для их обнаружения в современных микроэлектронных САПР [1]–[2] предусмотрены средства их обнаружения.

Как правило, большее количество ошибок возникает на нижних уровнях проектирования. Это связано с тем, что отклонения от требуемых значений параметров объектов на этих этапах могут быть незначительными. Поэтому их сложнее отследить, чем, например, отклонение значений параметров верхнего структурного уровня проектирования, таких, как состав реализуемой системы или разрядность данных.

Как уже было сказано выше, ошибки по их количеству и возрастанию степени сложности обнаружения можно ранжировать следующим образом:

- структурно-топологические (изменение разрядности данных);

- схемотехнические (искажение схемы при разработке топологии);

- электрические (изменение параметров компонентов – длины и ширины каналов транзисторов, ширины шин);

- топологические (качество топологии);

- технологические (нарушение проектных норм).

Работа посвящена вопросам анализа и верификации геометрических моделей микроэлектронных объектов, и

в соответствующих ее разделах будут изложены результаты исследований авторов по созданию средств, отвечающих за мониторинг и анализ результатов различных этапов проектирования кроме структурнотопологического этапа (он не верифицировался в связи с относительной простотой анализа структурных параметров устройств по сравнению с огромным объемом рутинных действий по выявлению ошибок остальных типов).

# II. СРЕДСТВА РАСПОЗНАВАНИЯ КОМПОНЕНТОВ

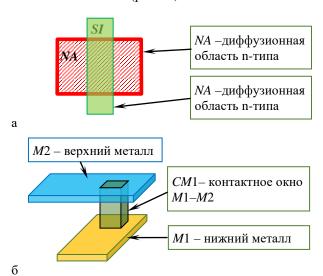

Поскольку топологические чертежи БИС представляют собой двумерные геометрические модели микроэлектронных трехмерных объектов, автоматизация процессов их верификации связана с проблематикой задач компьютерной геометрии. В связи с этим в составе средств мониторинга и анализа геометрических моделей необходимы программные объединения, модули, реализующие функции пересечения и вычитания геометрических фигур. Они позволят реализовать механизмы распознавания основных компонентов геометрических моделей (каналов транзисторов, контактов) путём анализа комбинаций геометрических фигур разных топологических слоях (рис. 1а).

Рис. 1. Примеры комбинаций геометрических объектов для основных типов выявляемых компонентов: а) транзистор n-типа (пересечение диффузионной n-области NA и поликремния SI; б) контакт между нижним (M1) и верхним (M2) металлами.

Например, транзистор n-типа (рис. 1, a) распознается как пересечение фигур в слоях NA (диффузионная

область n-типа) и SI (поликремний), а контакт между нижним (M1) и верхним (M2) металлами (рис. 16) — как комбинация налагающихся друг на друга фигур в слоях M1 и M2 при наличии внутри них контактного окна (прямоугольника в слое CM1).

# III. Схемотопологическая и электрическая верификация геометрических моделей

Схемотопологическая и электрическая верификации геометрических моделей микроэлектронных объектов нижнего уровня (ячеек) тесно связаны друг другом. Действительно, проверка значений электрических параметров компонентов возможна лишь в том случае, когда сами эти компоненты идентифицированы. То есть установлено соответствие между компонентами электрической и геометрической модели.

Для автоматизации решения этой задачи используются различные подходы на основе графовых нейронных сетей [3]–[4], на основе гиперграфовых сверточных сетей [5] и на основе алгоритмов поиска изоморфизма графов [6]. В отличие от использования нейросетей поиск изоморфизма графов гарантирует точное сопоставление электрической и геометрической модели.

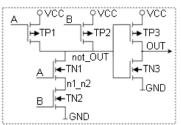

В связи с этим в своих исследованиях [7]–[8] авторы ориентировались на методы анализа изоморфизма графов. При этом перед верификацией необходимо построить два графа электрической модели объекта: один по исходному описанию, задаваемому в текстовом формате *Spice-netlist* (рис. 2), а второй по его геометрической модели.

#### Netlist

TP1 VCC A not\_OUT VCC

TP2 VCC B not\_OUT VCC

TP3 VCC not\_OUT OUT VCC

TN1 not\_OUT A n1\_n2 GND

TN2 n1\_n2 B GND GND

TN3 OUT not\_OUT GND GND

Рис. 2. Пример графического описания электрической модели микроэлектронного объекта (схема ячейки 2-AND) и его текстового описания (netlist)

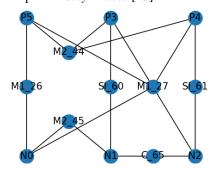

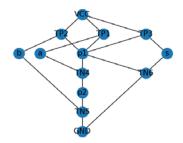

Сначала основании анализа комбинаций на геометрических объектов в различных топологических осуществляется распознавание элементов геометрической модели. Потом по геометрической модели строится граф, который можно назвать «схемотопологическим», так как в нем отображаются все компоненты топологии ячейки. Для снижения сложности задачи сравнения графов на его основе строится электрический граф. Эта процедура осуществляется объединения электрически связанных межслойными контактами шин в разных топологических слоях. Описания упрощенного графа, извлеченного из И графа электрической представляются в формате JSON, удобном для описания На рис. 3 и рис. 4 приведены графы, построенные по геометрической модели ячейки 2-AND и по ее электрической модели.

Для использования в разработанных средствах автоматической верификации были реализованы четыре алгоритма анализа изоморфизма, считающиеся наиболее эффективными: один из вариантов алгоритма Ласло

Бабая [10], алгоритм Вейсфейлера-Лемана [11], алгоритм VF2 [12], алгоритм Nauty-Traces [13].

Рис. 3. Граф ячейки 2-AND, построенный по ее геометрической молели

Рис. 4. Граф ячейки 2-AND, построенный по ее электрической модели

В netlist-описании помимо номеров (или имен) узлов схемы содержатся электрические характеристики транзисторов, основными из которых являются длина и ширина канала. Это позволяет проводить не только схемотопологическую, но и электрическую верификацию топологии и схемы: верификацию с учетом параметров их компонентов.

Помимо принципиального несоответствия топологии компонентов геометрической и электрической моделей схеме можно локализовать ошибки в коммутации компонентов. Для этого нужно вернуться к «схемотопологическому» графу и, пройдя по цепочке коммутационных компонентов, выявить отсутствие какого-либо из них (шины или контакта).

# IV. ТЕХНОЛОГИЧЕСКАЯ ВЕРИФИКАЦИЯ ЯЧЕЕК ГЕОМЕТРИЧЕСКИХ МОДЕЛЕЙ

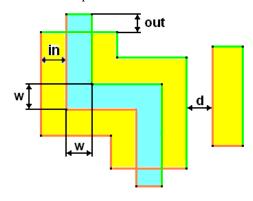

При проверке геометрической модели ячейки на соответствие проектным нормам параметрам технологической реализации (проектным нормам) осуществляется анализ ее компонентов и их взаимного расположения на следующие параметры (рис. 5): минимально допустимую ширину (w), зазор (d), включение одного компонента в другой компонент (in), выход одного компонента за пределы другого (out).

Проверка осуществляется посредством анализа взаимного расположения левых и правых (или верхних и нижних) границ соседних или вложенных друг в друга компонентов геометрической модели. На рис. 5 они изображены разными цветами: левые и нижние границы – коричневым, а правые и верхние – зеленым. При этом учитываются и диагональные расстояния.

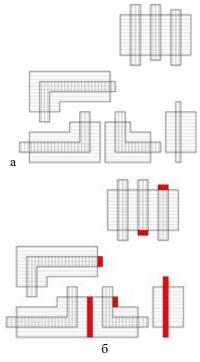

Информация о нарушении проектных норм выводится в текстовый файл с указанием типа ошибки и ее координат в топологии ячейки. Кроме этого формируется текстовая копия исходного файла описания геометрической модели в формате *CIF*, в которую добавляются компоненты, локализирующие место

обнаруженных нарушений технологических параметров, как это показано на рис. 6.

Рис. 5. Параметры геометрической модели микроэлектронного объекта, верифицируемые на соответствие вектору технологических параметров: минимально допустимые ширина (w), зазор (d), включение одного компонента в другой компонент (in), выход одного компонента за пределы другого (out)

Рис. 6. Пример результатов технологической верификации: а) геометрическая модель из исходного файла; б) геометрическая модель из итогового файла с выделением красным цветом выявленных нарушений вектора технологических параметров

# V. Анализ качества геометрических моделей

Традиционно критерием качества геометрической модели объекта считается ее площадь. Однако, из этого неясно насколько рассматриваемая геометрическая модель хороша, насколько она близка к идеалу, и каков вообще этот идеальный вариант реализации. Авторы предложили комплексный критерий [14]–[15], который основывается на соотношении вклада в площадь компонентов в зависимости от их степени значимости.

В соответствии с этим компоненты можно разделить на: функциональные (транзисторы), коммутационные (шины и контакты), технологические (карманы и контакты к карманам и подложке, области легирования). Очевидно, что чем больше доля основных компонентов и чем меньше доля вспомогательных компонентов, тем лучше топология. Исходя из этого, необходимо оценивать площади каналов транзисторов, стоковых-

истоковых областей транзисторов, межсоединений и свободных зон. Причем оценка соотношения этих параметров должна быть дифференциальной. Это позволит выявлять части топологии, требующие переработки, то есть превратит средства анализа из средств статистической оценки результатов проектирования в рабочий инструмент проектировщика.

Первые исследования в этой области были посвящены разработке методов и средств мониторинга и анализа пространственных характеристик ячеек. В данной работе речь идет о новой версии программных средств автоматизированной оценки качества топологии «Layout Monitoring», позволяющих анализировать топологию не только ячеек, но и сложных иерархических фрагментов.

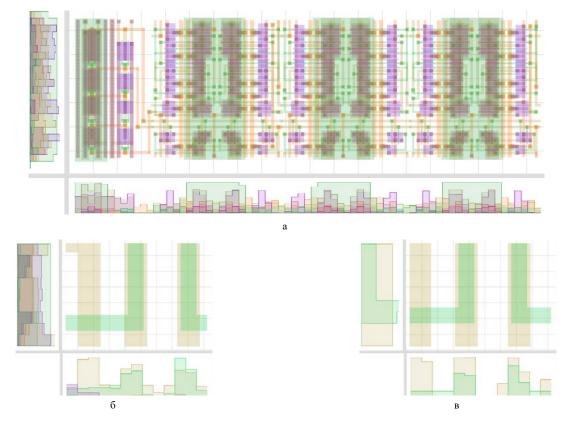

На рис. 7 представлено окно визуализации топологии с вертикальной и горизонтальной гистограммами результатов анализа одноразрядного сумматора с разным шагом дискретизации.

Рис. 7. Окно визуализации топологии автоматизированной системы «Layout Monitoring» с гистограммами одноразрядного сумматора с разным шагом дискретизации

Пользователь может настроить гистограммы на отображение интересующих его комбинаций топологических слоев. Например, для отображения информации о каналах транзисторов (пересечение компонентов В слоях активных областей поликристаллического кремния) или о межсоединениях (объединение компонентов в слоях поликремния и металла).

Как уже было сказано В новой версии автоматизированной системы «Layout Monitoring» стало сложных возможным оценивать топологии иерархических блоков, причем в разных режимах. В качестве примера на рис. 8 представлены окна визуализации топологии иерархического фрагмента БИС с гистограммами.

Рис. 8. Окна визуализации автоматизированной системы «*Layout Monitoring*» с гистограммами регулярного иерархического фрагмента (а) и его кластера с простым увеличением (б) и с построением гистограммы непосредственно для кластера (в)

На рис. 8а приведено гистограмма иерархического фрагмента, а на рис. 86 и на рис. 86 представлены гистограммы для кластера топологии. На рис. 86 кластер увеличен до размера окна, а слева и снизу от него отображены соответствующие кластеру фрагменты вертикальной и горизонтальной гистограмм всего иерархического фрагмента. На рис. 86 приведено окно визуализации для другого режима работы, в котором строятся непосредственно гистограммы для кластера отображаемого В окне топологии иерархического блока БИС.

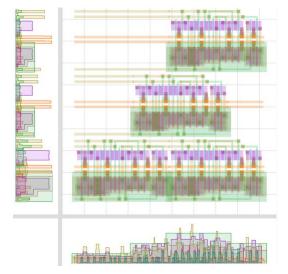

Кроме того, в новой версии автоматизированной системы «Layout Monitoring» стало возможным оценивать качество геометрических моделей сложных иерархических нерегулярных блоков (рис. 9).

Рис. 9. Окно визуализации топологии автоматизированной системы «Layout Monitoring» с гистограммами нерегулярного иерархического фрагмента

#### VI. ЗАКЛЮЧЕНИЕ

На основании анализа особенностей верификации геометрических БИС разработаны моделей оригинальные методы и средства анализа соответствия (топологии) геометрической модели исходному описанию объекта (электрической схеме) и средства анализа соответствия геометрической модели вектору технологических параметров (проектным нормам). Для анализа качества геометрических моделей предлагается комплексный критерий, и описываются оригинальные программные средства мониторинга, анализа и оценки характеристик моделей микроэлектронных объектов и иерархических систем разного уровня сложности (в том числе нерегулярных).

Направлением дальнейшего развития могу быть исследование и разработка методов повышения производительности средств мониторинга, анализа и верификации путем учета особенностей описания геометрических моделей сложных микроэлектронных объектов.

### Список литературы

- [1] https://cadence-ds.ru

- [2] https://www.synopsys.com

- [3] Alrahis L., et al. GNN-RE: Graph Neural Networks for Reverse Engineering of Gate-Level Netlists // IEEE Trans. Comput.-Aided Design Integr. Circuits Syst. 2022. Vol. 41, № 8. P. 2435–2448.

- [4] Teliti A. Graph neural networks for topology recognition of ams integrated circuits: Ph.D. dissertation. Torino: Politecnico di Torino, 2023

- [5] Li B., Wang S., Chen T., Sun Q., Zhuo C. Efficient Subgraph Matching Framework for Fast Subcircuit Identification // Proc. 6th ACM/IEEE Symp. Machine Learning for CAD (MLCAD). Salt Lake City (Snowbird), USA, 2024. P. 1–7.

- [6] Ohlrich M., Ebeling C., Ginting E., Sather L. SubGemini: Identifying Subcircuits Using a Fast Subgraph Isomorphism Algorithm // Proc. 30th Int. Design AutomationConf. (DAC'93). New York: ACM, 1993. P. 31–37.

- [7] Миронов С.Э., Андреев Л.Е. Схемная верификация топологии ячеек БИС // Известия СПбГЭТУ «ЛЭТИ». 2013. № 2. С. 38–40.

- [8] G.A. Mamedov, S.E. Mironov and A.I. Tikhonova, "Application of Graph Isomorphism Analysis Algorithms for Scheme-Topological Verification of Complex Microelectronic Objects," 2024 XXVII International Conference on Soft Computing and Measurements (SCM), Saint Petersburg, Russian Federation, 2024, pp. 1-5, doi: 10.1109/SCM62608.2024.10554089.

- [9] S. Varfolomeev, A.V. Lepov and S.E. Mironov, "Verification of Electrical and Geometric Models Using Graph Isomorphism Checking Algorithms," 2025 XXVIII International Conference on Soft Computing and Measurements (SCM), Saint Petersburg, Russian Federation, 2025, pp. 118-122, doi: 10.1109/SCM66446.2025.11060105.

- [10] Babai L. Graph Isomorphism in Quasipolynomial Time: Extended Abstract // Proc. 48th Annu. ACM Symp. Theory of Computing (STOC'16). New York: ACM, 2016. P. 684–697.

- [11] Зыков А.А. Темы в теории графов. М.: Наука, 1990. С. 191–192.

- [12] NetworkX Developers, "VF2 Algorithm–NetworkX 1.11 Documentation." [Online]. Available: https://networkx.org/documentation/networkx-

- 1.11/reference/algorithms.isomorphism.vf2.html. [Accessed: Apr. 7, 2025].

- [13] McKay B.D., Piperno A. Nauty and Traces User's Guide (Version 2.5). Canberra: Computer Science Department, Australian National University, 2013.

- [14] S.E. Mironov and L.E. Andreev, "Monitoring of Spatial Characteristics of Two-dimensional Models of Three-dimensional Microelectronic Objects," 2022 XXV International Conference on Soft Computing and Measurements (SCM), Saint Petersburg, Russian Federation, 2022, pp. 72-75, doi: 10.1109/SCM55405.2022.9794860.

- [15] S.E. Mironov and A.V. Vyachin, "Method and Decision Support System on Redesign of LSI Cells Topology," 2024 XXVII International Conference on Soft Computing and Measurements (SCM), Saint Petersburg, Russian Federation, 2024, pp. 75-78, doi: 10.1109/SCM62608.2024.10554214.

- [16] S.E. Mironov and A.V. Vyachin, "Method and Decision Support System on Redesign of LSI Cells Topology," 2024 XXVII International Conference on Soft Computing and Measurements (SCM), Saint Petersburg, Russian Federation, 2024, pp. 75-78, doi: 10.1109/SCM62608.2024.10554214